FPGA全加器(VHDL)

一位全加器实验报告

一、实验目的与要求

通过此实验让用户逐步了解、熟悉和掌握FPGA开发软件Quartus II的使用方法及VHDL的编程方法。学习用VHDL语言以不同方式来描述1位全加器及电路的设计仿真和硬件测试,同时结合按键输入,在硬件设备上实现全加器的功能。

二、实验设备

- SmartSOPC+实验箱

- 装有QuartusⅡ的PC机

- JTAG下载器

三、实验内容

本实验的内容是建立一个1位全加器。具体内容包括:

(1)使用Quartus II建立工程、编写程序;

(2)进行波形仿真验证;

(3)进行硬件测试。

通过SmartSOPC实验箱上的按键KEY1~KEY3输入信号,分别为A.B和Cin,并通过,LED1 ~LED3指示相应的状态。输出Sum和Cout通过LED7和LED8指示(灯亮表示输人或输出为“1”)。

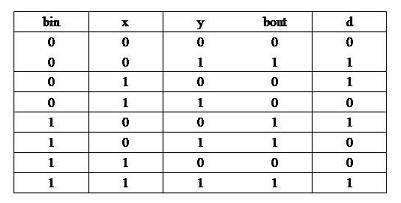

一位全加器真值表:

四、实验步骤

-

启动QuartusII建立一个空白工程,然后命名为add.qpf。

-

新建VHDL源程序文件add.vhl,输人程序代码并保存,然后进行综合编译。若在编译过程中发现错误,则找出并更正错误,直至编译成功为止,并生成图形符号文件add.bdf。

-

波形仿真验证,步骤如下:

-

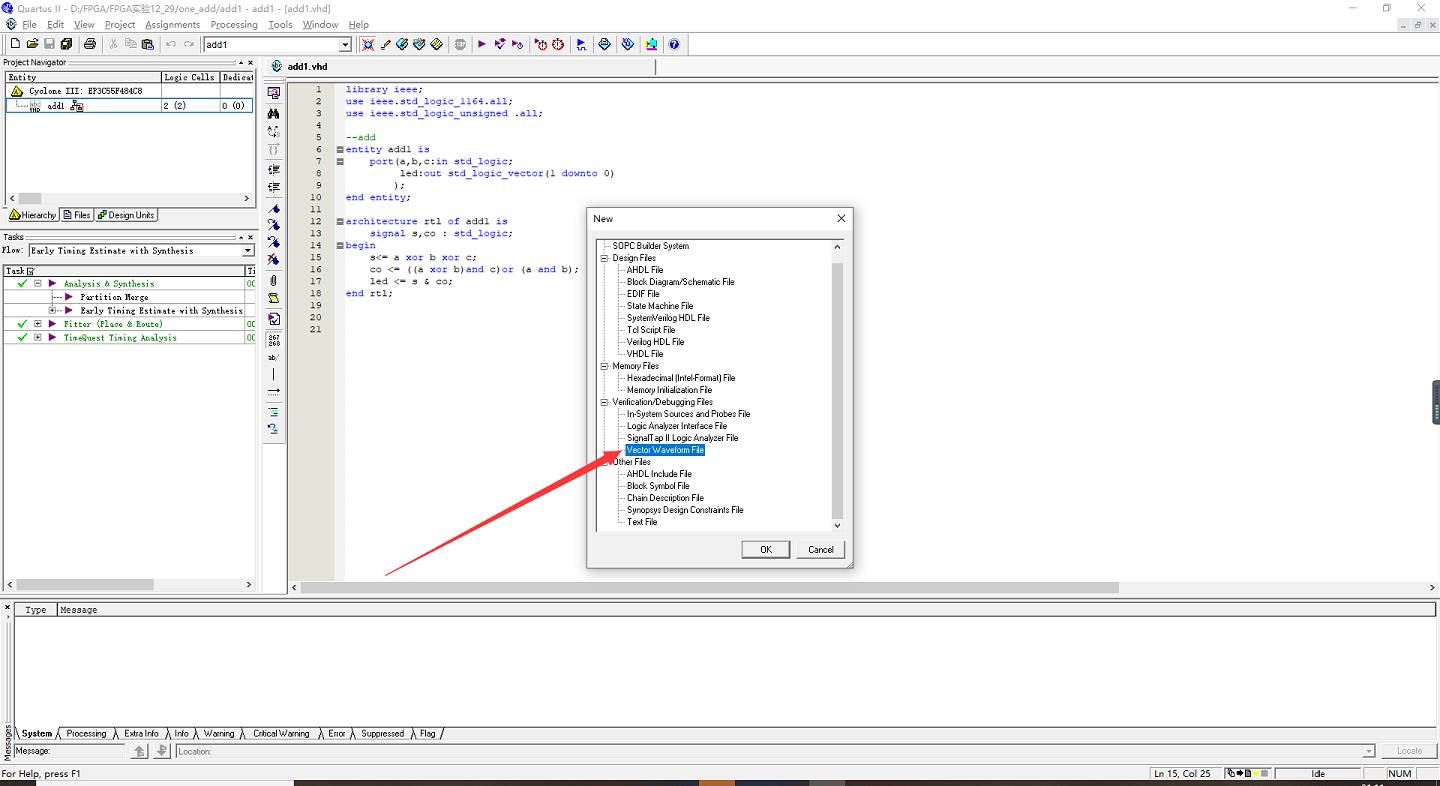

在QuartusII主界面中选择File→New命令,打开新建文件对话框,在该对话框中选;择Other Files选项卡,从中选择Vector Waveform File,如图3. 38所示。单击OK关闭建立一个 空的波形编辑器窗口

创建文件:

wave文件:

-

在如图所示的Name选项卡内双击鼠标左键,弹出下图所示对话框。在如该对话框中单击NodeFinder按钮,弹出如图对话框。

-

点击list列出节点并添加节点

-

为输入信号添加随机信号,便于仿真

-

点击仿真,保存,得到仿真结果,对比真值表,如下图

-

-

仿真正确无误后,分配程序引脚,下载程序

五、设计程序

一位加法器程序较为简单,设计思路主要为读取按键端口,带入逻辑计算后输出加法器值,具体程序如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned .all;

--add

entity add1 is

port(a,b,c:in std_logic;

led:out std_logic_vector(1 downto 0)

);

end entity;

architecture rtl of add1 is

signal s,co : std_logic;

begin

s<= a xor b xor c;

co <= ((a xor b)and c)or (a and b);

led <= s & co;

end rtl;

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

六、实验结果及分析

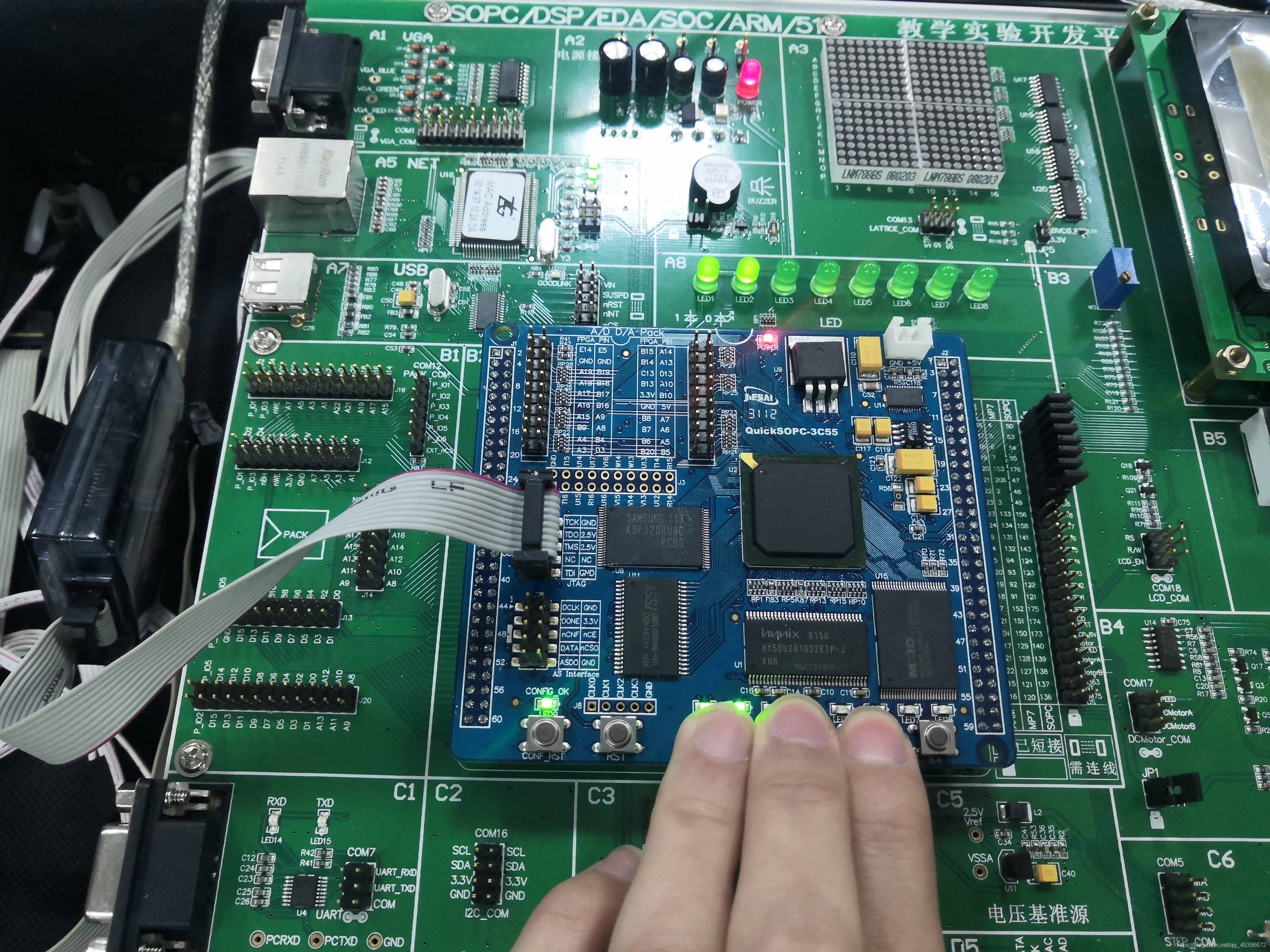

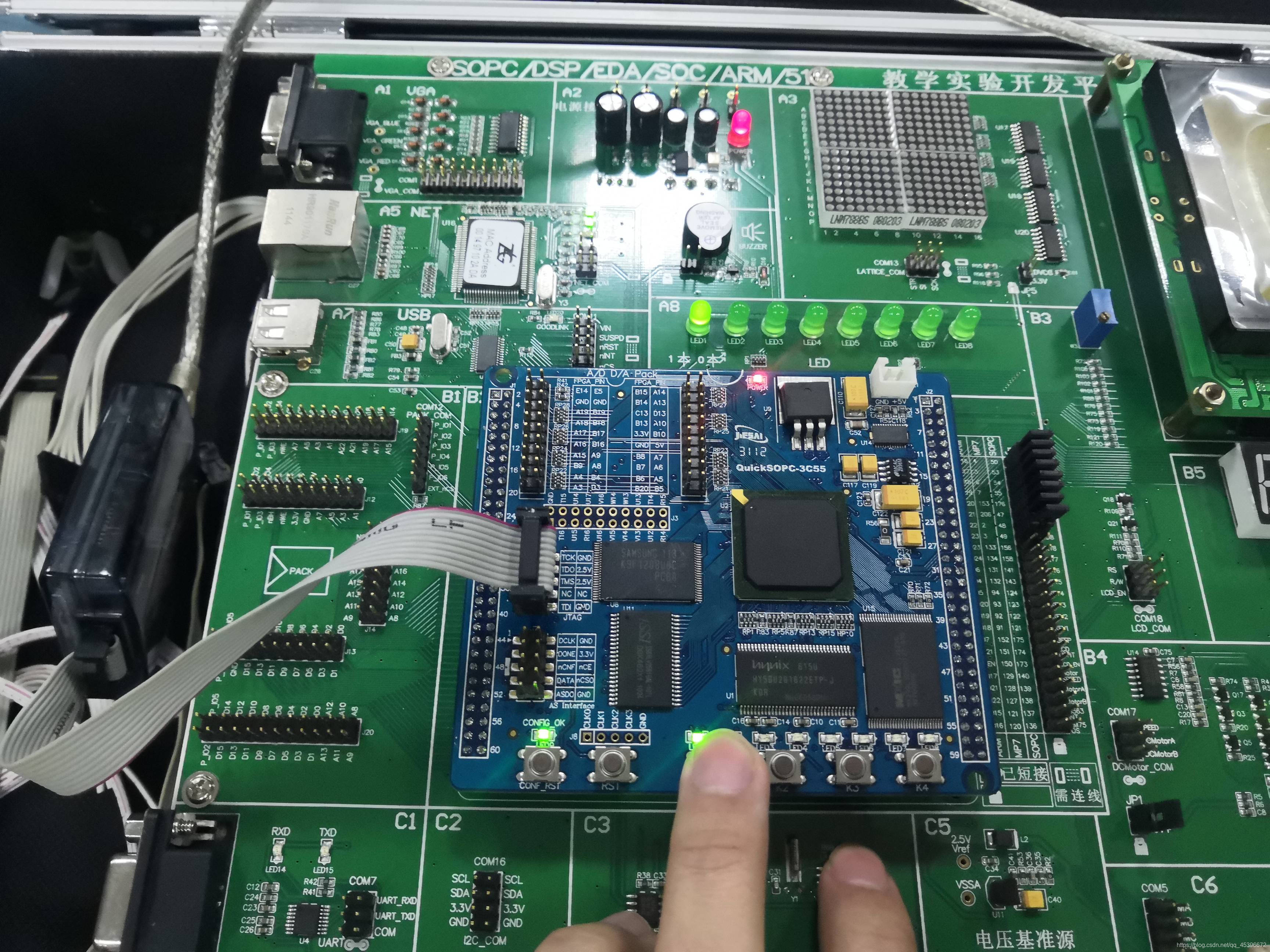

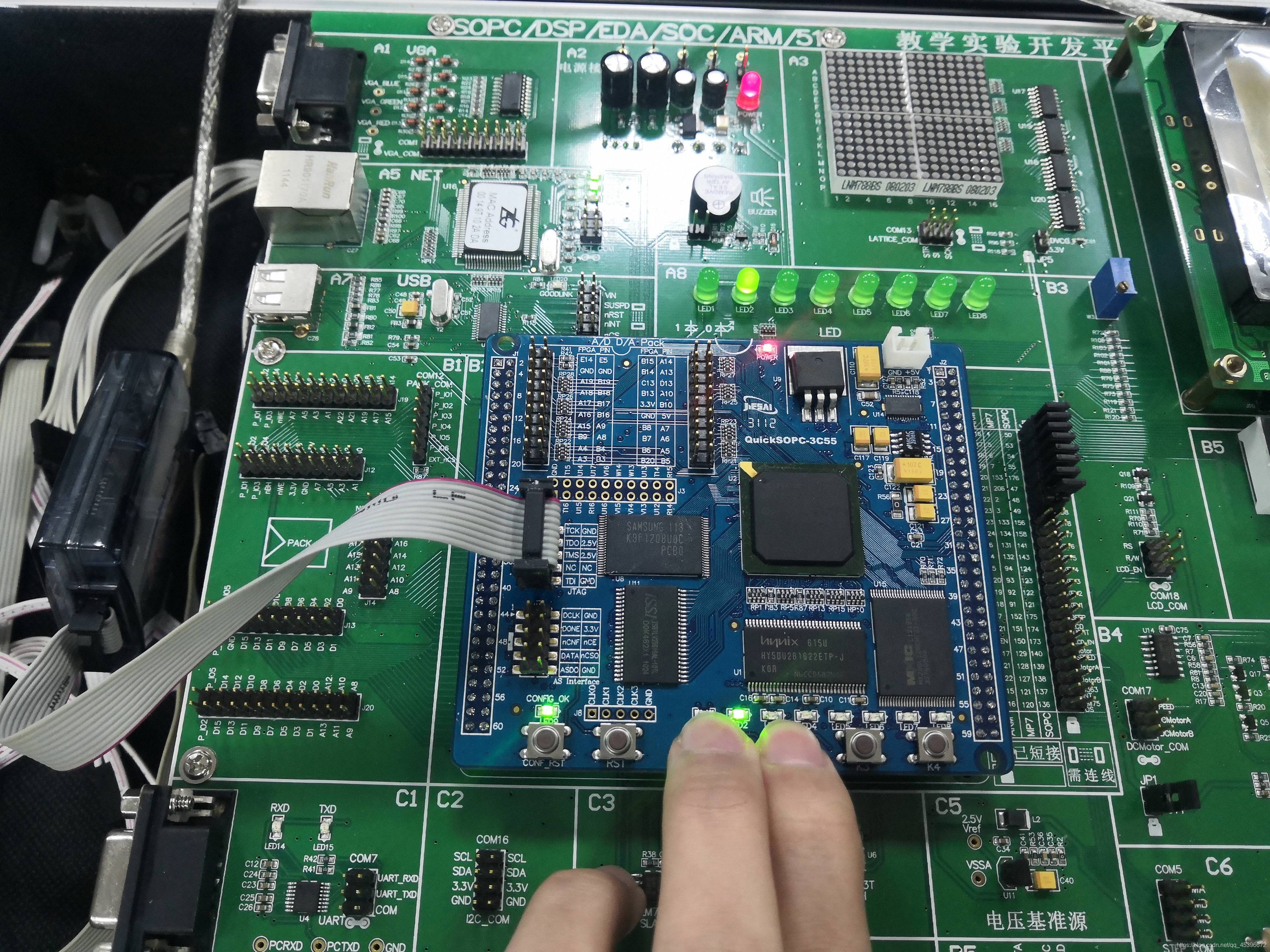

实验图片:

- 进位为:1 1 1

- 进位:1 0 0

- 进位:1 1 0

结果分析:

对下载后程序进行测试,其实验现象和理论仿真一致,程序达到设计目标。

文章来源: blog.csdn.net,作者:JeckXu666,版权归原作者所有,如需转载,请联系作者。

原文链接:blog.csdn.net/qq_45396672/article/details/113029430

- 点赞

- 收藏

- 关注作者

评论(0)