HDLBits 系列(44)状态机补录

前言

今天补一个状态机的题目,也是这个系列的题目之一,但是由于之前对题目有点疑惑,今天得到博友反馈,让我明白了这个题目的意思,记录一下。

原题链接

原题复现

Consider a finite state machine that is used to control some type of motor. The FSM has inputs x and y, which come from the motor, and produces outputs f and g, which control the motor. There is also a clock input called clk and a reset input called resetn.

The FSM has to work as follows. As long as the reset input is asserted, the FSM stays in a beginning state, called state A. When the reset signal is de-asserted, then after the next clock edge the FSM has to set the output f to 1 for one clock cycle. Then, the FSM has to monitor the x input. When x has produced the values 1, 0, 1 in three successive clock cycles, then g should be set to 1 on the following clock cycle. While maintaining g = 1 the FSM has to monitor the y input. If y has the value 1 within at most two clock cycles, then the FSM should maintain g = 1 permanently (that is, until reset). But if y does not become 1 within two clock cycles, then the FSM should set g = 0 permanently (until reset).

(The original exam question asked for a state diagram only. But here, implement the FSM.)

Module Declaration

module top_module ( input clk, input resetn, // active-low synchronous reset input x, input y, output f, output g

);

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

题目解析

当时没有明白的还是这一句话:

While maintaining g = 1 the FSM has to monitor the y input. If y has the value 1 within at most two clock cycles, then the FSM should maintain g = 1 permanently (that is, until reset). But if y does not become 1 within two clock cycles, then the FSM should set g = 0 permanently (until reset).

更确切的是这句话:

While maintaining g = 1 the FSM has to monitor the y input. If y has the value 1 within at most two clock cycles, then the FSM should maintain g = 1 permanently (that is, until reset).

是接下来的两个时钟周期内,有一个y为1就可以了,之后的输出永久为1,如果没有一个为1,则永久为0.

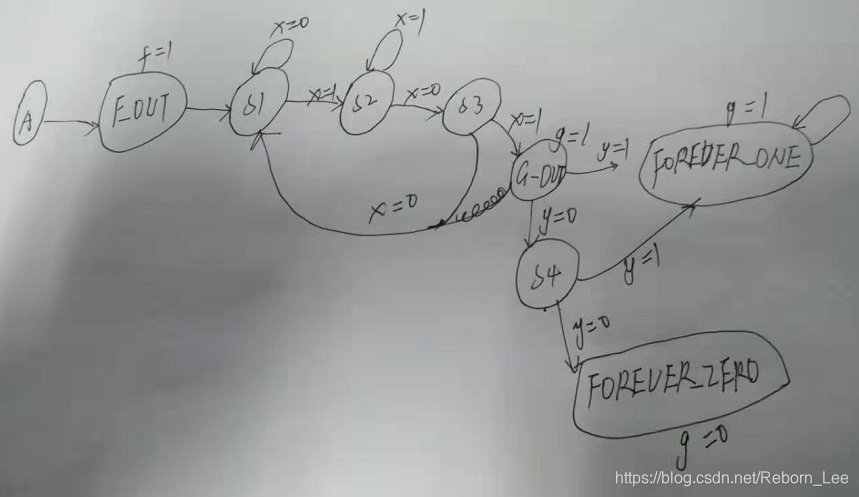

根据题目,给出状态转移图:

状态转移图

设计文件

module top_module ( input clk, input resetn, // active-low synchronous reset input x, input y, output f, output g

); parameter A = 4'd0, S1 = 4'd1, S2 = 4'd2, S3 = 4'd3, S4 = 4'd4; parameter G_OUT= 4'd5, FOREVER_ONE = 4'd6, FOREVER_ZERO = 4'd7; parameter F_OUT = 4'd8; reg [3:0] current_state; reg [3:0] next_state; always@(posedge clk)begin if(resetn == 1'b0)begin current_state <= A; end else begin current_state <= next_state; end end always@(*)begin case(current_state) A:begin next_state = F_OUT; end F_OUT:begin next_state = S1; end S1:begin next_state = x ? S2 : S1; end S2:begin next_state = x ? S2 : S3; end S3:begin next_state = x ? G_OUT: S1; end G_OUT:begin next_state = y ? FOREVER_ONE : S4; end S4:begin next_state = y ? FOREVER_ONE : FOREVER_ZERO; end FOREVER_ONE:begin next_state = FOREVER_ONE; end FOREVER_ZERO:begin next_state = FOREVER_ZERO; end default:begin next_state = A; end endcase end assign f = (current_state == F_OUT); assign g = (current_state == S4 || current_state == G_OUT || current_state == FOREVER_ONE); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

文章来源: reborn.blog.csdn.net,作者:李锐博恩,版权归原作者所有,如需转载,请联系作者。

原文链接:reborn.blog.csdn.net/article/details/103570177

- 点赞

- 收藏

- 关注作者

评论(0)